반도체 생산성이 완벽합니까?

더 이상의 생산성 향상은 없습니다.

완전한.

철저한.

당신은 그것을 믿지 않습니까? 그렇다면 다시 생각하십시오.

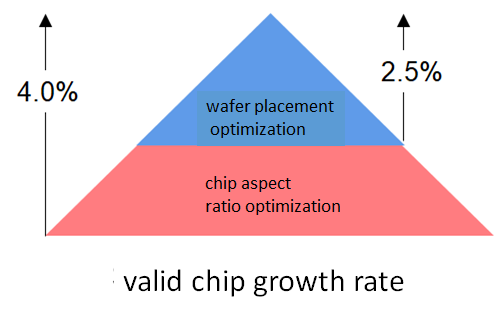

칩 종횡비와 웨이퍼 배치를 개선하면 생산성을 더욱 높일 수 있습니다.

넌 할 수있어.

이 사이트에서만 제공되는 기술은 세계에서 유일합니다.

웨이퍼 당 칩 수가 감소함에 따라 효과가 증가합니다.

예를 들어, 칩 크기가 큰 CMOS 센서를 제조 할 때 또는 소 직경 기판 인 SiC와 같은 화합물 반도체를 사용하는 경우 현저한 효과를 기대할 수 있습니다.

더 이상의 생산성 향상은 없습니다.

완전한.

철저한.

당신은 그것을 믿지 않습니까? 그렇다면 다시 생각하십시오.

칩 종횡비와 웨이퍼 배치를 개선하면 생산성을 더욱 높일 수 있습니다.

넌 할 수있어.

이 사이트에서만 제공되는 기술은 세계에서 유일합니다.

웨이퍼 당 칩 수가 감소함에 따라 효과가 증가합니다.

예를 들어, 칩 크기가 큰 CMOS 센서를 제조 할 때 또는 소 직경 기판 인 SiC와 같은 화합물 반도체를 사용하는 경우 현저한 효과를 기대할 수 있습니다.

수율 만 좋으면 충분합니까?

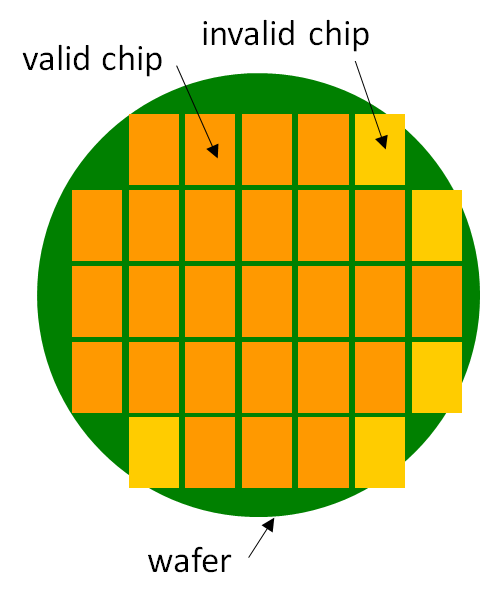

반도체 산업은 수율 산업이라고합니다. 소량의 먼지와 먼지는 수율을 크게 감소시키기 때문에 입자 대책에 많은 돈이 필요합니다. 사실, 좋은 칩의 수는 본질적이며 수율이 중요하다는 것이 분명합니다. 그러나 하나의 웨이퍼에서 절단 할 수있는 칩의 수 (유효 칩 수)도 동일하게 중요합니다.결함이없는 칩 = 수율 x 유효한 칩

그러나 유효한 칩 수를 늘리는 사람은 거의 없습니다. 그 이유는 다음과 같습니다.① 유효한 칩의 수는 지역에 따라 결정되었으며 나중에 늘리거나 줄일 수 없다고 생각했습니다

② 정사각형이 항상 최고의 칩 모양 인 것은 아닙니다

③ 내 임무는 수율을 높이는 것이므로 유효한 칩 수를 늘리는 데 관심이 없습니다

④ 유효한 칩 수의 증가에 대한 제안이 제안되었지만 감독자의 허가를 얻을 수 없었습니다

아직도, 당신은 이익을 그리워합니까?

보는 것은 믿는 것입니다. 살펴보고 계산해보십시오.① 칩 종횡비 최적화:

칩 종횡비와 유효한 칩 번호 사이의 관계를 나타냅니다 → 연산 서비스

② 웨이퍼 배치 최적화 :

유효한 칩 수를 최대화하는 웨이퍼 중심 위치를 나타냅니다. → 연산 서비스

참고) 일반적으로 메뉴 막대의 태그에서 이동합니다.(칩 종횡비 최적화・칩 종횡비 최적화).

유효한 칩 수가 100 개 미만이고 레이아웃 디자인이 아직 수행되지 않은 경우 종횡비 최적화부터 시작하십시오. 평균 4.0 % 생산성 향상을 기대할 수 있습니다.

레이아웃 디자인이 완료되면 노출 프로세스에서 레이아웃을 최적화하십시오. 평균 2.5 % 생산성 향상을 기대할 수 있습니다.

이 사이트를 사용하여 큰 이익을 내십시오.

더 많은 돈을 벌 수있는 기회를 간과하지 마십시오.

그래도 사용에 대한 우려가 있다면,

부담없이 문의하기.

그런 다음이 서비스를 사용하는 효과는 다음 페이지에 설명되어 있습니다.

다음 페이지 사용 효과

(2023 년 10 월 29 일 업데이트) 개발의 역사

처음에는 스테퍼 액세서리 소프트웨어였습니다.2001 년 봄이되었습니다. 제품 기획부의 K 씨가 저를 방문하여 "정말 최적의 웨이퍼 배치를 실현하는 소프트웨어를 만들고 싶습니다."라고 말했습니다. 그는이 소프트웨어를 사용하여 노출 장비 판매를 홍보하고자했습니다.

기술의 가치는 스테퍼 시장보다 컸습니다.

노광 장치의 품질도 성능에 관계없는 이야기 였기 때문에 처음에는 거절 할 생각이었습니다. 그러나 문제 해결에서 만들어지는 가치가 연간 1 조엔 규모이다 듣고 생각이 바뀌 었습니다. "노광 장치의 전 세계 매출보다 큰 잖아." 갑자기 의욕이 가득했습니다.

기술 개발이 발전했습니다.

확실히 어려운 문제가 있었지만, 최적화 특유의 「요령」을 알고있었습니다. 따라서 기존의 방법보다 충분히 뛰어난 것을 발명하는 자신감은있었습니다. 실제로 약 반년 후에는 유효 칩의 최대 값을 구하는 알고리즘을 발명하고 소프트웨어를 만들고 2002 년에는 특허도 출원했습니다. 이 발명은 유효 칩의 최대 값과 그것을 실현하는 하나의 배치를 보여했습니다. 그러나 인바릿도 영역이 줄어도 최대 수를 유지할 수 최적 배치가 없습니다. 그래서 더욱 연구를 진행 최적 배치에 선수를 쓰는 방법을 완성하고 2004 년에 특허 출원했습니다.

사용 가능성이 닫혔습니다.

그런데 의뢰인 K 씨는 이동해 버렸습니다. 솔루션과 소프트웨어는 완성했지만, 실용화 할 수없는 상태가되어있었습니다. 그리고 장비 개발 실패로 사업이 위기에 빠지자 2009 년에 최첨단이었다 침수 노광 장치에서 철수하기로 결정했습니다. 또한 권리화 된 특허도 포기하게되었습니다.

이번에는 종횡비 최적화라는 주제가 등장했습니다.

그런데 2011 년이 된 어느 날, 반도체 소자의 설계 개발하고있는 부서의 O 씨로부터 전화가있었습니다. 내 특허를 찾은 것 같아서, 그 소프트웨어를 사용하고 싶다는 것이 었습니다. 조금이라도 회사의 이익에 공헌 할 수 있다면 생각, O 씨의 요구에 부응하고 동시에 그 이용 목적을 물었습니다. O 씨에 따르면, 유효 칩 수를 극대화하는 최선의 칩 종횡비를 조사하고 있다는 것이 었습니다. 그러나 O 씨는 종횡비 최적화 요청을하지 않았습니다. 나도 다른 과제에 임하고있었습니다. 그런 이유로 회사에서 아무것도하지 않고 있으며했습니다. 하지만이 정년 퇴직 한 후 작업 보려고했습니다.

은퇴 후 챌린지 테마가되었습니다.

나는 중도 입사 27 년에서 60 세 정년을 맞이했습니다. 이제, 나는 칩 종횡비 최적화 알고리즘 개발에 몰두했습니다. 대부분의 아이디어는 대체로 완성했습니다. 그래서 정말 프로그래밍하고 테스트 할뿐이었습니다. 2017 년 6 월, 제가 개인적으로 특허 출원했습니다. 2018 년 9 월, 나는 무료 클라우드 컴퓨팅 서비스를 시작했습니다.